纳米增材制制工艺可大幅降低芯片出产成本

作者:和记AG 浏览:

团队暗示,上述工艺流程存正在几个较着错误谬误。起首是成本昂扬。目前,每年的运营成本也高达10亿美元。其次是采用现无方法制制芯片需要半年到一年时间,测试后的点窜同样需要这么长时间。第三是该流程能耗极高。因为制制过程需要正在实空和高温前提下进行,一个典型晶圆厂的耗电量取5万个家庭的耗电量相当。

据美国官网近日报道,该校研究团队开辟出一种新工艺及打印设备,能正在纳米标准上更高效地制制先辈的电子产物和芯片,其制形成本仅为保守手艺的1%。

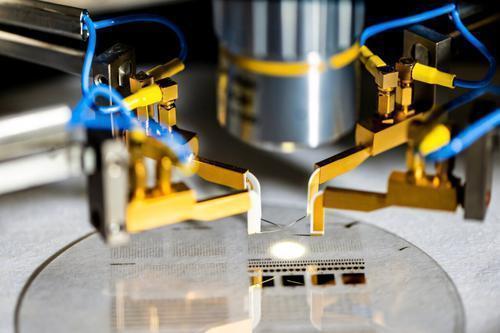

为了降低电子产物和芯片的制形成本,团队开辟出一种增材“自下而上”的制制工艺。保守方式就像正在石头上凿刻出新事物;而新方好像用黏土建制新物体。只需正在合适按需放置材料即可。这些材料可利用很是小的颗粒快速堆积,可正在一分钟内建制出小至25纳米的布局。新方式不只产量高,并且成本极低。

上一篇:红木原材价钱行情(两极分化严沉)